Description

SystemVerilog for Verification Part 1: Fundamentals is published by Udemy Academy. The VLSI industry is divided into two popular branches: system design and system verification. Verilog, VHDL are still the popular choices of most design engineers working in this field. However, initial functional verification can be done with the hardware description language. The hardware description language has limited capabilities to perform code coverage analysis, test cases, etc., and in fact, it is sometimes impossible to do this with HDLs. Hence specialized verification languages such as SystemVerilog become the main choice for design verification.

The object-oriented nature of SystemVerilog enables features such as inheritance, polymorphism, etc., and adds capabilities to find critical design bugs that HDL simply cannot find. Verification is definitely more complex and interesting compared to the design of a digital system, and hence, unlike Verilog, it incorporates a large number of OOP constructs. SystemVerilog is one of the most popular choices among verification engineers for digital system verification. . In this article, we will introduce you to the most common techniques used to write SystemVerilog Testbench and perform Chipset Verification. This course is designed so that the student can understand everything. Ultimately, practice is the key to becoming an expert.

What you will learn

- SystemVerilog principles for RTL verification

- OOPS Fundamentals for the FPGA Engineer

- Principles of limited random validation methodology

- Principles of layered test architecture

- Create Generator, Driver, Monitor, Scoreboard, Environment Classes

- Array, Queue, Dynamic Array, Tasks and SV methods

- Interprocessing communication and SV randomization

Who is this course suitable for?

- Anyone want to migrate to SystemVerilog Testbench for RTL validation

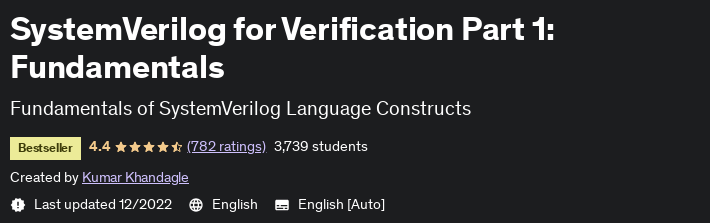

Course specifications SystemVerilog for Verification Part 1: Fundamentals

- Publisher: Udemy

- teacher : Kumar Khandagle

- English language

- Education level: all levels

- Number of courses: 211

- Training duration: 13 hours and 57 minutes

Head of the course chapters on 2022-12

Course prerequisites

- Fundamentals of Verilog and Digital Electronics

Pictures

Sample video

Installation guide

After Extract, view with your favorite Player.

English subtitle

Quality: 720p

download link

File(s) password: www.downloadly.ir

Size

3.65 GB